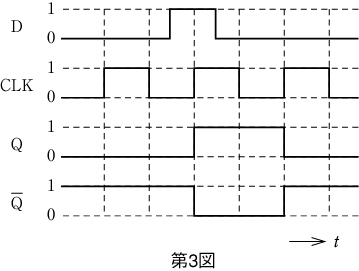

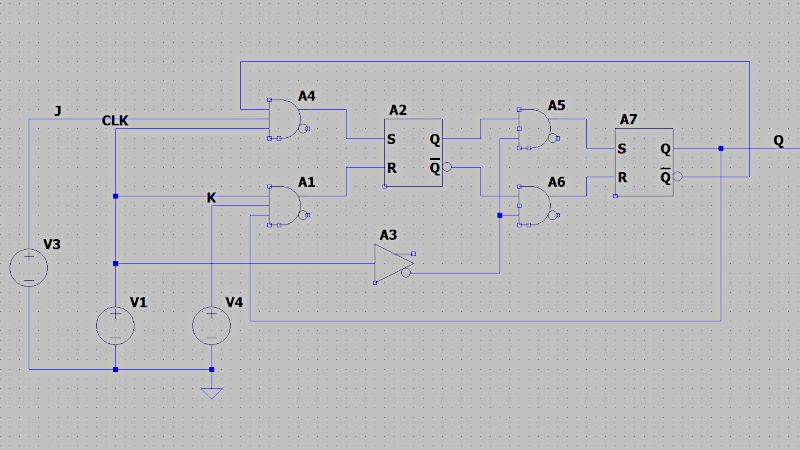

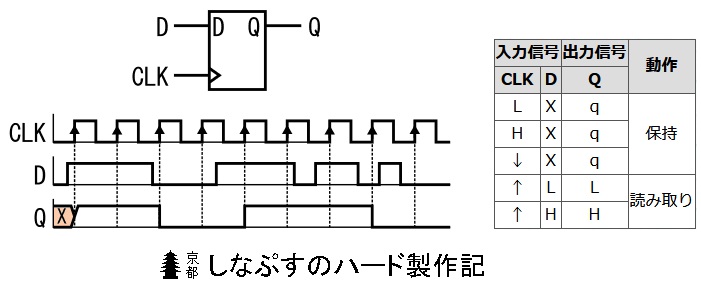

Hardware Description Language)のうち,よく使用されるVHDLとVerilog HDLの二つのHDLの基本文法を説明します.ちょっとした違いを発見しながら読み進めると面白いでしょう. ソフトウェア・プログラミングで使用するCやJava 以下の図は、各端子における入力されたパルス信号と出力されたパルス信号です。 各端子における入力されたパルス信号と出力されたパルス信号 Q1 と Q2 から出力されるパルス信号にて電圧が低いを0、電圧が高いを1とすると、回路の真理値表は以下の上の図の回路で、 組合せ回路は q=1 のとき (s,r)=(0,1) を、q=0のとき (s,r)=(1,0)を出力する クロックの幅がやや広かった と仮定します。 初期状態は q=0 です。 クロックが与えられた時点でs入力が 1 となり、t1 後に フリップフロップがセットされます(q=1となります)

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

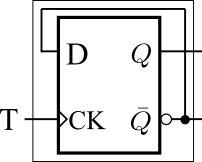

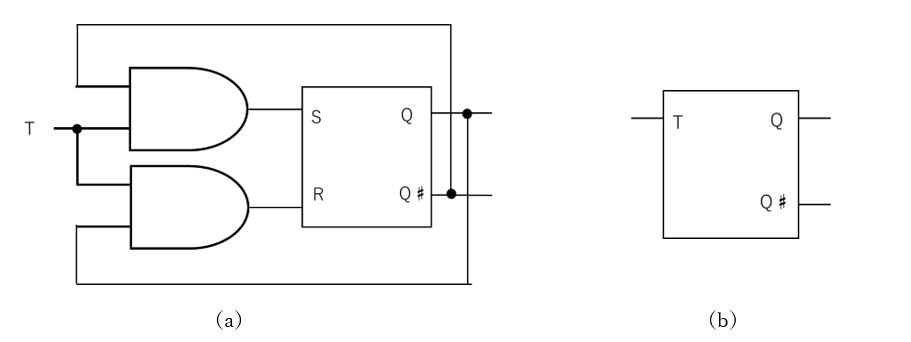

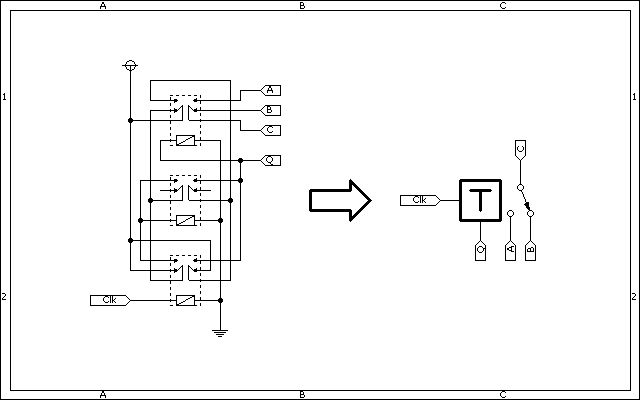

T-ff 回路図

T-ff 回路図-回路構成は少し複雑 クロックはキャリーの伝播 遅延時間とffのスイッチング 遅延時間で決まる (非同期式より遅い) カウント値が安定する のに必要な時間が短い 出力にハザードが発生しない 用途 低速の回路 高い周波数のクロック の分周回路東芝cmosデジタル集積回路 シリコン モノリシック tc74hc393ap,tc74hc393af dual binary counter tc74hc393a は、シリコンゲートcmos 技術を用いた高速 cmos 2 回路入りbinary counterです。cmos の特長である 低い消費電力で、lsttl に匹敵する高速動作を実現できます。

Digital Circuit Lab4

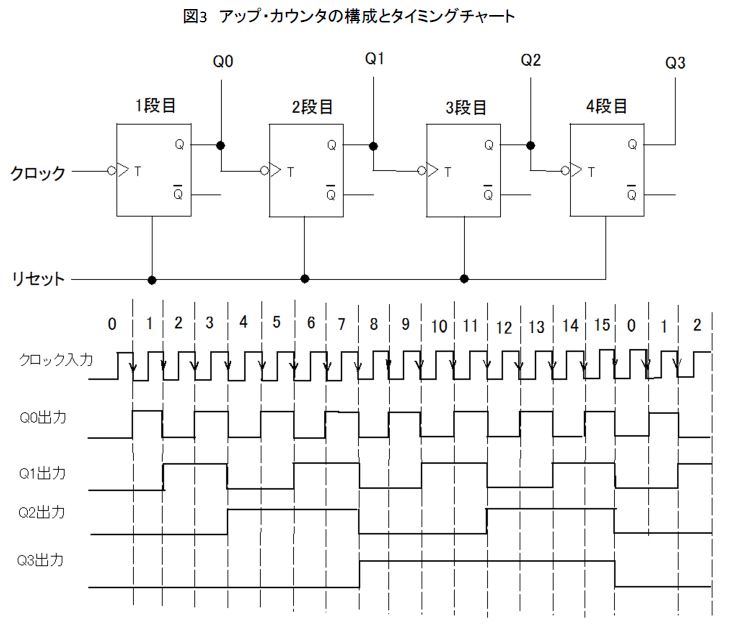

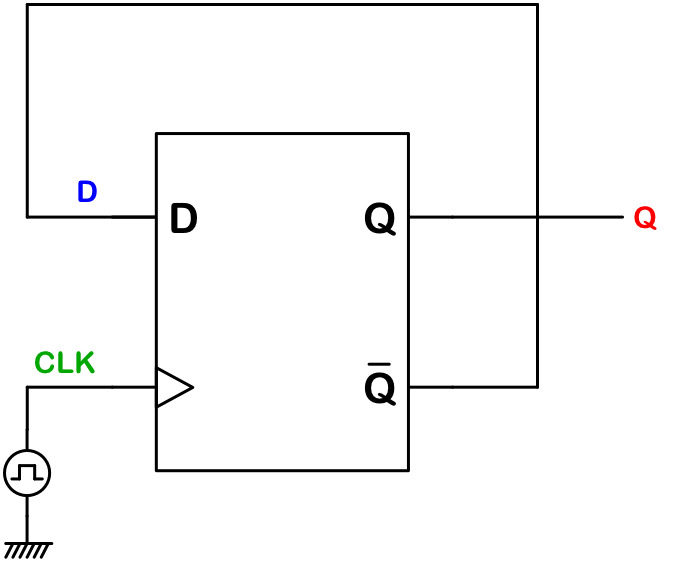

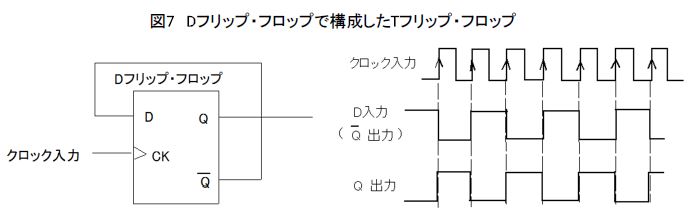

電子回路ドリル II(18) MONOist 問題16 DFFでカウンタを作る : 完全マスター! 電子回路ドリル II(18) » 08年05月22日 00時00分 公開00/8/7,11「vlsi設計・夏の学校」 ディジタル回路設計の基礎 4 同期回路とは? 時間方向を同期パルス(クロック)により、量子化 (ディジタル化)した回路 クロックにより、クロックとの間のタイミングを考 慮するだけでよくなる。次式のDFFの特性方程式を用いて,順序回路を構成する. つまり,状態遷移図の「次の状態Y」をDFFのQ n1と考えれば良い 以上より,DFFの入力方程式は 4) 回路図 Q n1 =D Y=Q n1 DFF:入力Dが次の状態Q n1 入力方程式: FFの入力を現状態yと入力xで記述.この入力により

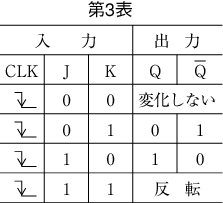

9 4 同期カウンタ回路についての復習 0から9までの10つの情報を表現するには4ビットが必要であるから, JKフリップフロップを4つ使用する. 状態の変化(遷移)を表すテーブルを作成する. ここで,Q 1n, Q 2n, Q 3n , Q 4n はフリップフロップ1 (FF1)から機器の省電力化と設計の簡易化に貢献する電圧共振回路用ディスクリートIGBT発売について 機能安全に対応したマルチ出力車載向け汎用システム電源ICの製品化について ホールセンサー不要でクローズドループ速度制御機能内蔵、 三相ブラシレスモーター Tフリップフロップ 真理値表 答えがわかりません解答お願いします (1)有効数字2桁で次の量を表せ a v b s c F dHz (2)電荷g=−12μCと電荷Q=−06μCが距離r=18cm離れている時の力の大きさと種類を求めよ (3)正電荷2x10^6Cと正

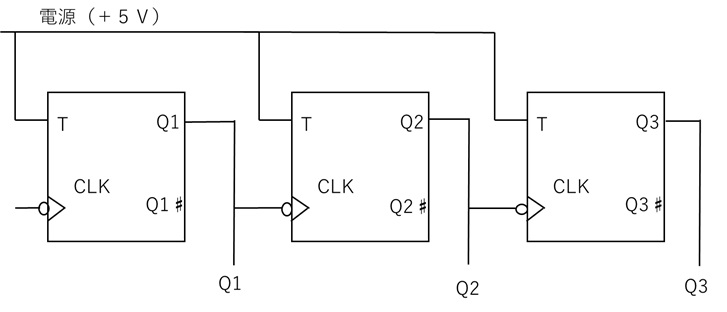

論理図 1/2 tc4013bp/bf 絶対最大定格 (注) 項目 記号 定格 単位 電源 電圧 vdd vss − 05~vss v 入力 電圧 vin vss − 05~vdd 05 v 出力 電圧 vout vss − 05~vdd 05 v 入力 電流 iin ±10 ma 許容 損失 pd 300 (dip)/180 (sop) mw 動作 温度 topr −40~85 °c 保存 温度 tstg −65~150 °c下に tffを用いた2進カウンタ の 回路図 を示します。 なお、このTFFは第2章で紹介した パルス型(AC型) ではなく、 入力 T の立ち上り直後に出力 Q が反転する DC型のTFF であることに注意して帰還を持つインバータ回路(2個の場合) 2つの安定状態を持つ インバータの個数と安定/発振の関係 奇数個の場合:発振 偶数個の場合:2つの安定状態を持つ hlhlhl

フリップフロップ

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

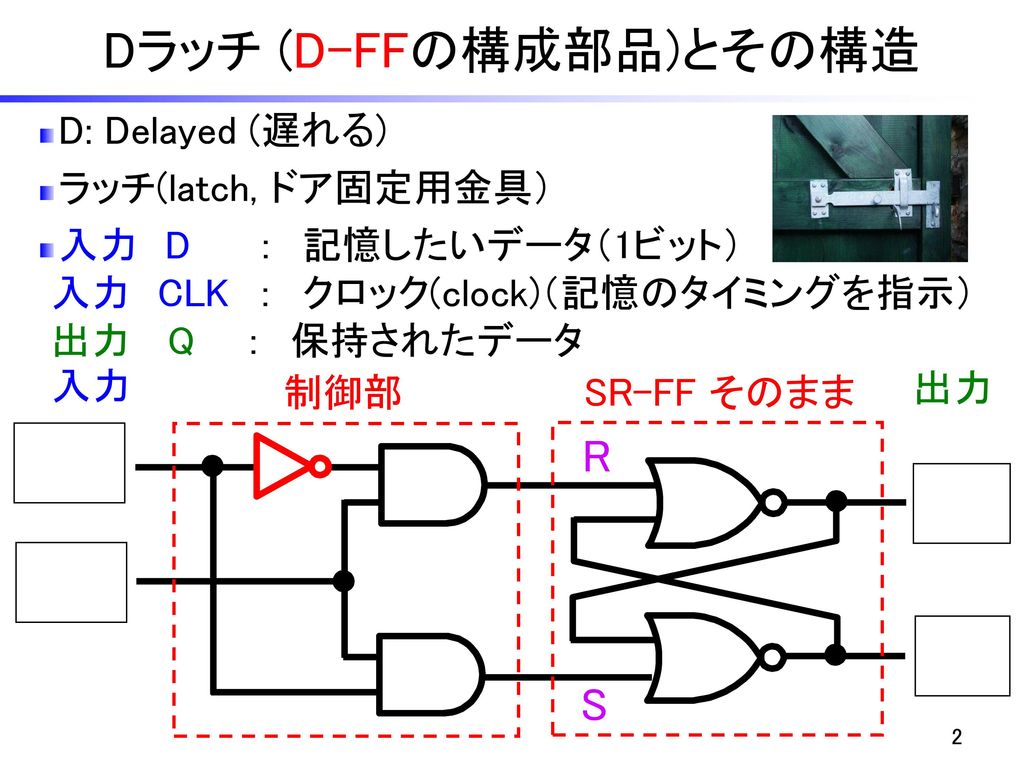

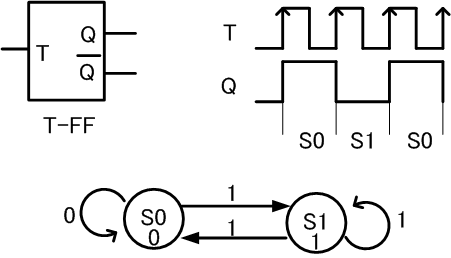

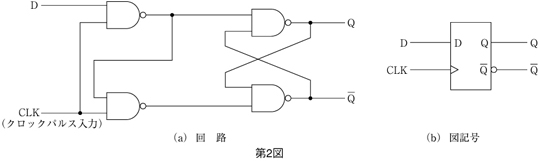

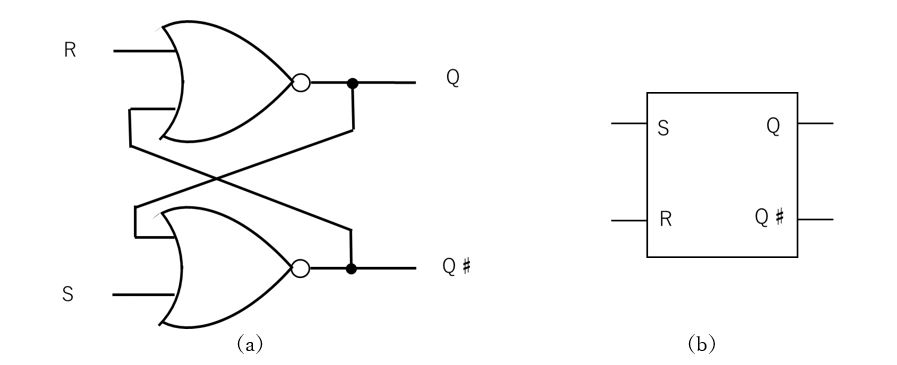

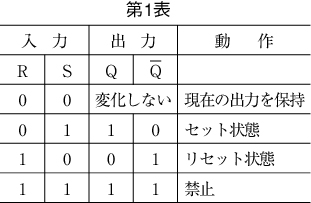

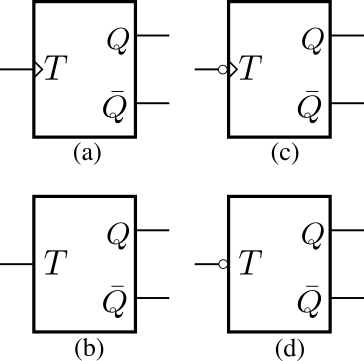

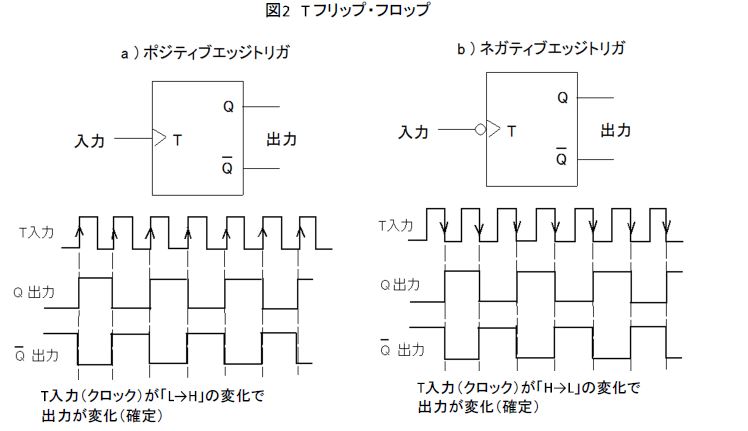

Tフリップフロップは、入力信号の制御で出力信号が反転 (トグル)するフリップフロップです。 図1は回路図でTフロップフロップを表すシンボルです。 入力端子としてT、出力端子として Q と Q ― を持ちます。 Q ― は Q の反転値が出力されます。回路で、中央処理装置内部のレジスタやキャッシュメモリなど、記憶を司る回路に使用されてい ます。ここでは、構造が最もシンプルな図430 のRS フリップフロップ4について解説します5。 図中のS (Set) とR (Reset) は入力、Q とQ は出力を表します6。 電子回路ドリル II(16) MONOist 問題14 JKFFのタイムチャート : 完全マスター! 電子回路ドリル II(16) » 08年05月01日 00時00分 公開

フリップフロップ

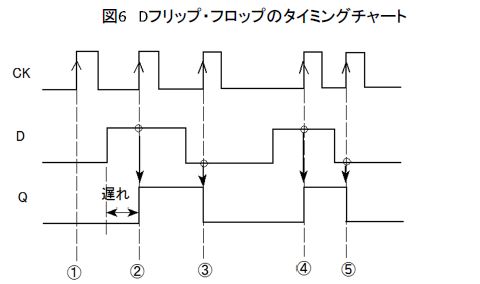

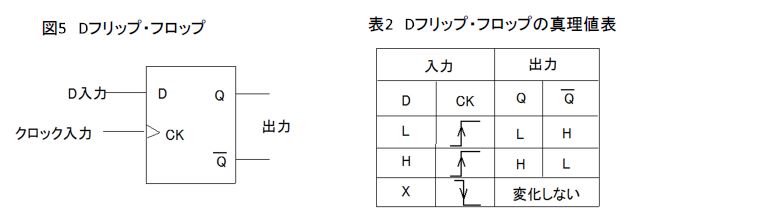

第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt Download

Mick's Manuals (無線機/受信機など) 下記機種のマニュアルが欲しい!という方はこちらから御連絡下さい ご不要のマニュアル売却希望方もお気軽に!! 図2 t型フリップフロップ(カウンタ回路) 図2はtffの入力端子を電源に接続し、ハイレベルに固定したもので、clkパルスが2個入力されるたびにqとq♯に1個のパルスが出力される様子を示しています。(赤で示した部分) tffを直列に接続した回路 図3はtffを3個直列に接続した場合の回路構成で、図4はそのタイムチャートです。ゲート回路による tff の回路図 RSFF を用いて TFF を構成すると次に示す回路となる。 RSFF を用いて構成した TFF の回路図

フリップフロップ Wikipedia

1

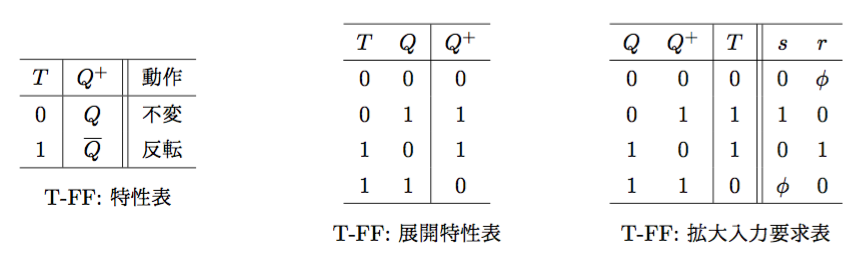

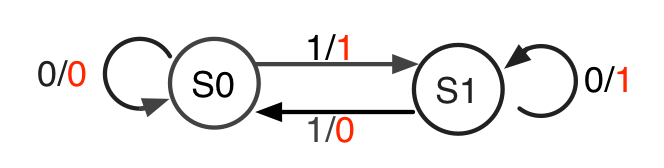

順序論理回路は内部状態と入力の組み合わせで出力が決まる。 これを記述するのに、状態遷移図を作成する。状態遷移図に基 づき指定された動作を行う順序論理回路を設計する。 2.順序論理回路 組み合わせ論理回路では 出力=f(入力)組み合わせ回路 この回路を ff 設計する 外部入力 i1, i2, , im 外部出力 o1, o2, , on 状態 q1, q2, , qk 同期式回路の設計 1 入力(i1, i2, im),出力(o1, o2, on),状 態(q1, q2, qk)を決める 2 状態遷移図を描く 3 状態遷移表を作成する 4 拡大入力要求表を作成する 5論理回路 摂大・鹿間 k j q q ck 0 遅延 遅延 ネガティブエッジトリガjkffの動作(sn74lvc112a) case #21:q 0,q 1(ck 0) ( 配線を省略)clr,pre 0 0 0 1 0 0 0 0 0 0 1 0 1 1 1 1 j, k 入力によらずリセット状態を保持 論理回路 摂大・鹿間 k j q q ck 0 遅延 遅延

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

01 号 分周回路 Astamuse

64 同期式順序回路 Synchronous sequential logic circuit •ディジタル回路の表現方法 Ø真理値表 Ø論理式,論理方程式 Ø回路図 Øハードウェア記述言語(HDL hardware description language) Øタイミングチャート Ø状態遷移図(clr回路なし,jkff3段)2/2 回路構成 ffa 出力qとffbのck 接続 ja に接続 ka=jb=kb=kc=1 (vcc) and 入力 ,出力jc ckffa,ffcに接続 強制clrのない5進カウンタである qc qa,qb q j q k >ck clr ck vcc(1) qa q j q k >ck clr qb clr ffa ffb q j q k >ck clr qc ffc 論理回路 摂大・鹿間 tffによるT ff は2 個の信号が入力されると元の状態に戻る回路である. タイミングチャート t q (ポジティブエッジトリガーの場合) 横軸を時間にし, 縦軸を各変数の 値としたグラフ これをn 個接続して2n 進カウンター (計数回路)を作ることができる. q cl t q1 t q2 t q3 ・・・・ q q

真理値表 の解説 しなぷすのハード製作記

Dフリップフロップ

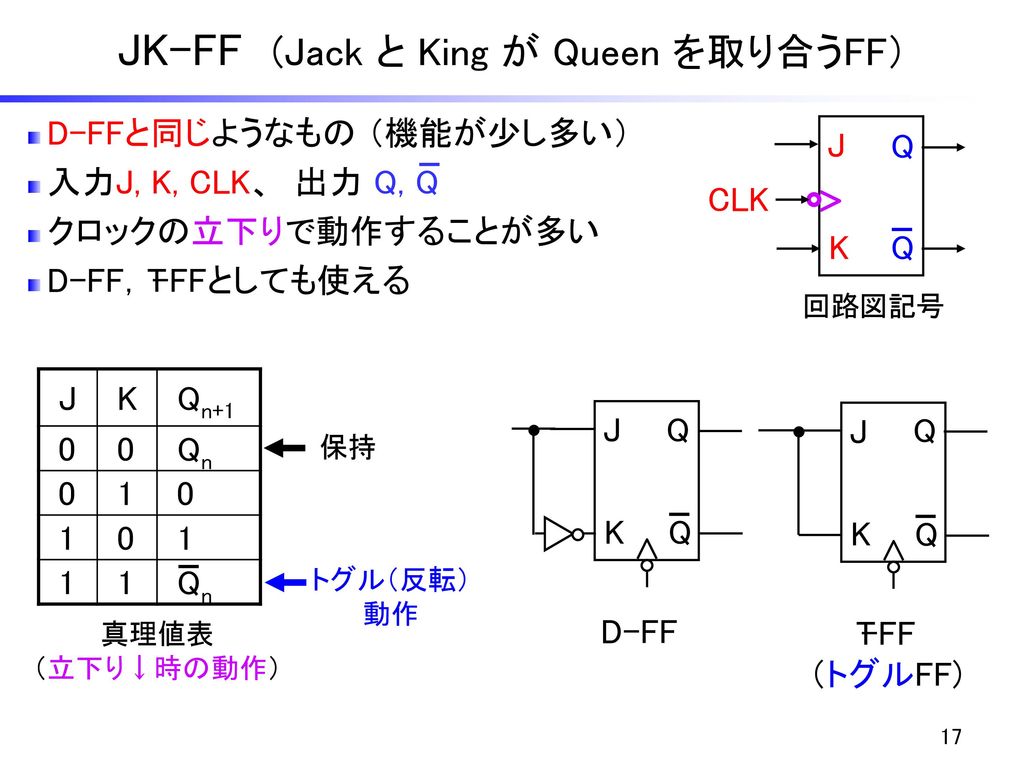

これより、上の中央の回路図が得られます。なお、この tff を簡略化した記号(図の下)で表すことがあります。 次に、この tff の タイムチャート を示します。 上の図で、入力信号 t = 1 の幅が狭いことに注意して下さい。T ff は2 個の信号が入力されると元の状態に戻る回路である. タイミングチャート t q (ポジティブエッジトリガーの場合) 横軸を時間にし, 縦軸を各変数の 値としたグラフ これをn 個接続して2n 進カウンター (計数回路)を作ることができる. q cl t q1 t q2 t q3 ・・・・ q q順序回路の設計と動作解析2 70 42 jkフリップフロップの特性方程式によりカウンタ回路を設計する方法 a)jkフリップフロップの特性方程式 下記に示すjkフリップフロップの動作表をもとにしてjkフリップフロップの特性方程式 を求める。 jkフリップフロップの動作表

トランジスタの見た夢 その2 トランジスタの見た夢

Chap10

33 tff の応用:分周器・・・1個のtffで周波数が1/2になる t q q t _ q q _ t q q _ t1 t2 t3 q1 q2 q3 p p q1 q2 q3 注)前段の変化が次々に影響が波及⇒直流駆動型、非同期式カウンタなど6進カウンタ回路を tff を用いて作成するときの回路図を示しなさい。 入力中で3個連続した1を見つける回路を実現しなさい。 自動販売機の状態遷移図において、S1からの遷移 100/01 の表わす内容を説 TFFの動作、回路図 TFFの動作、回路図 http//wwwquantphcstnihonuacjp/~kuwamoto/kuwamoto/pdf こちらの一番右上のTFFの原理図ですがこの通りに回路を作ってもうまく動作しません。 確かに動作の軌跡を追っていくと、入力Tのクロックを立ち上げたままだと永遠に出力が安定しないので、QまたはQ'からANDの入力に信号が戻るよりも前に入力T

フリップフロップについて質問です Jk Ffでt Ffを作った Yahoo 知恵袋

アップダウンカウンタの制作 基礎編 マルツセレクト

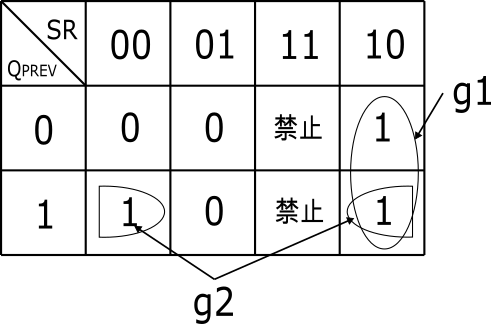

3 j 1 k 1 q 1 q 0 q 1 q 0 a 00 01 11 10 a 00 01 11 10 00 11 j 0 k 0 q 1 q 0 q 1 q 0 q 1 q 0 a 00 01 11 10 a 00 01 11 10 a 00 01 11 10 00 0 11 1 出力z 図3 jkff の入力j 1,k 1,j 0,k 0 を求めるためのカルノー図 演習5演習4 で得られた論理関数から,同期式3 進カウンタになるように図4 の結線きる同期式順序回路が多く用いられている。 5 考察 この実験を通して、同期式カウンタの設計法と同期式tff,dff,jkff の動作の特徴および利用法を学ぶことができた。 6 感想 実験は回路が入り組んで分かりにくかったが、どうにかミスをせずに完成T ff (t フリップフロップ ) を、図 5267 に示します。 t ff は、それ自体の ic 製品は、存在しませんが、各種の ff 応用回路の ic に利用されています。 図 5267 t フリップフロップ

2 原理

Computer Archtecture

14 周波数測定 27 2 j 入力がh のときは、出力q がh となる。 3 k 入力がh のときは、出力q がl となる。 4 j, k ともにh のときは、出力q が反転する。 例えば、図125 左のネガティブエッジ形jkff の入力端子j, k, c にそれぞれ、図のよ うなパルス波形が入力された場合を考える。ネガティブエッジ形2 2 2 jk ff jkフリップフロップは,図2に示すような回路で,j,k入力は rs ffのs,r入力と同様の働きをし,さらにrs ffで禁止されている入力の 組み合わせ(r=s="1")に対しても動作し,出力が反転する.ただし,このffは クロックパルスckを必要とする.すなわち,jおよびk入力に信号が加えられた だけ TFF フリップフロップ の一つ。 Tフリップフロップ、Tタイプ、あるいは「トグル」と呼ばれ、入力があるたびに保持内容が反転する。 バイナリカウンター や リップルカウンター は、このフリップフロップで作られる。

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 レーダー 基礎理論編

状態遷移図 石丸技術士事務所 ディジタル技術資料

( 1 ) ( ) s r q t q t s r q t rsffの回路構成(1-1) 2番目の式に ド・モルガンの 法則を適用 r s q q rsffは,norを使って以下の回路で与えることができる.14年12月1日 修正: 10年8月3日 公開 内田智久 Esys, IPNS, KEK 回路設計未経験者向けに必要最低限のVerilogHDL文法を解説した入門書です。 専門家向けに書かれた市販書籍は情報が多すぎるため、回路設計初心者からみると最低限何をどのように使えば良いのか分かりません。Created Date AM

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

情報画像学実験ii 実験1 論理回路

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

順序回路

論理回路 Logic Circuit Kanetaiの二次記憶装置

Chap10

フリップフロップ

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk クロックとタイミングチャートの書き方 工業大学生ももやまのうさぎ塾

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

Untitled Document

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

早わかり電子回路 順序回路とは フリップフロップの種類と同期の方法を学ぶ アイアール技術者教育研究所 製造業エンジニア 研究開発者のための研修 教育ソリューション

フリップフロップ回路とは 種類とそれぞれの動作をわかりやすく解説 Analogista

Computer Archtecture

フリップフロップ

デジタル回路設計入門

アップダウンカウンタの制作 基礎編 マルツセレクト

Tフリップフロップ 石丸技術士事務所 ディジタル技術資料

Jk Ffを使用してt Ff D Ffを作成せよという問題で特性 Yahoo 知恵袋

マスタスレーブtフリップフロップの問題を解いていたのですが だんだ 工学 教えて Goo

Jkv Gog6gepigm

問題14 Jk Ffのタイムチャート 完全マスター 電子回路ドリル Ii 16 Monoist

ラッチ回路 Wikipedia

早わかり電子回路 順序回路とは フリップフロップの種類と同期の方法を学ぶ アイアール技術者教育研究所 製造業エンジニア 研究開発者のための研修 教育ソリューション

フリップフロップ Wikipedia

フリップフロップ

Chap10

Tフリップフロップの変換 ニュース 21

Untitled Document

フリップフロップ

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 gmdss 基礎理論編

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

T Flip Flop 回路 マイクラポケット辞典

もっとも簡単な10進カウンタを作る

フリップフロップ

第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt Download

Tフリップフロップの意味 用法を知る Astamuse

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

1

まさはる S Weblog Prison Architect その3

論理回路 フリップフロップの動作原理 Youtube

Dフリップフロップ

フリップフロップ Wikipedia

カウンタとシフトレジスタ Cpuを作ろう 計算機教材とマイコンと電子工作 楽天ブログ

至急 論理回路の設計について T Ffをd Ffで設計せよ と Yahoo 知恵袋

Basicプログラミング

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

1

フリップフロップ Wikipedia

フリップフロップ

フリップフロップ Wikipedia

フリップフロップ

Dフリップフロップ の解説 1 しなぷすのハード製作記

早わかり電子回路 カウンタ回路とは 前提となる2進数の理解から丁寧に解説 アイアール技術者教育研究所 製造業エンジニア 研究開発者のための研修 教育ソリューション

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

マイクラ Tフリップフロップの解説と作り方 隠しドアなどにも Youtube

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

Digital Circuit Lab4

フリップフロップ

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

Tフリップフロップ 石丸技術士事務所 ディジタル技術資料

Digital Circuit Lab4

問題14 Jk Ffのタイムチャート 完全マスター 電子回路ドリル Ii 16 Monoist

Chap10

フリップフロップ回路 Youtube

論理回路 回路の解析 図1 に示す論理回路図が与えられている 入力はなく Okwave

アップダウンカウンタの制作 基礎編 マルツセレクト

アップダウンカウンタの制作 基礎編 マルツセレクト

1

フリップフロップ

Rsフリップフロップの論理式 石丸技術士事務所 ディジタル技術資料

フリップフロップ

うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk クロックとタイミングチャートの書き方 工業大学生ももやまのうさぎ塾

ミーリ マシンの状態遷移図例 石丸技術士事務所 ディジタル技術資料

回路図修正 電気電子技術研究室 Eet Lab

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

Flip Flop Circuit

アップダウンカウンタの制作 基礎編 マルツセレクト

記憶素子 フリップフロップ

フリップフロップ

0 件のコメント:

コメントを投稿